# MDG-MMS group Stage proposals on STM32 microcontrollers

#### Pasquale Buttà

MDG-MMS Group MCD Catania Design Director

### MDG-MMS Group

#### Supporting ST target markets

Automotive

Healthcare |

Industrial/Smartgrid

Security

Consumer

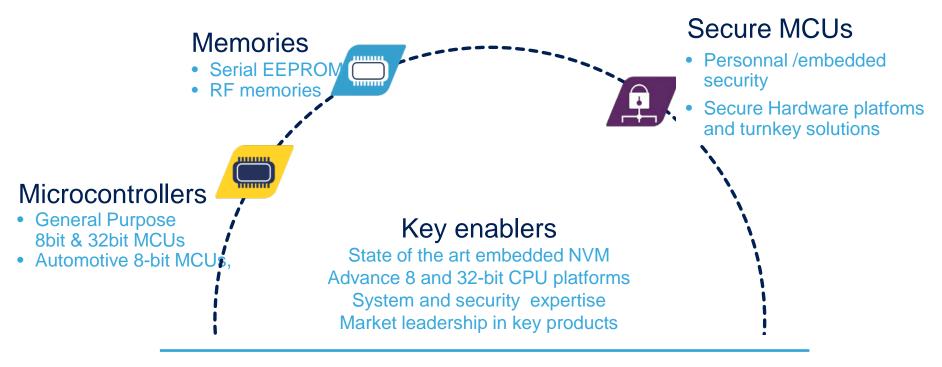

### General Purpose MCUs

A Wide range of Product sales Types embedding a rich set of Digital & Analog Peripherals Enabling selection flexibility on Embedded Flash size as well as performances

Real-time performance

Efficiency ™.

ART Accelerator™.

Chrom-ART

Accelerator™.

CCM-SRAM.

L1-Cache

Multi-AHB bus matrix,

Excellent real-time

Zero-wait state

execution performance

from Flash

Outstanding power efficiency

Dynamic Power 40 – 150 uA/Mhz Stop down to

< 1 uA Stand By down to < 300 nA

Shutdown downto < 20 nA Reach Set of peripherals

USB-OTG High speed, Ethernet, CAN, DFSDM, HR timer, LCD-TFT controller, SRAM interface, crypto/hash processor, true RNG\*, PGA, 16-bit ∑ADC and 12-bit ADC (up to 5 MSPS), external memory

interface, CEC, SAI

Maximum integration

Reset circuitry, voltage regulator, internal RC oscillator, PLL, WLCSP packages

Smart Industry

City

Over 4 Billion Devices Delivered to Broad Range of Markets

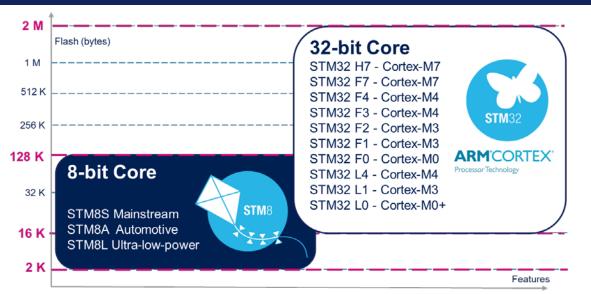

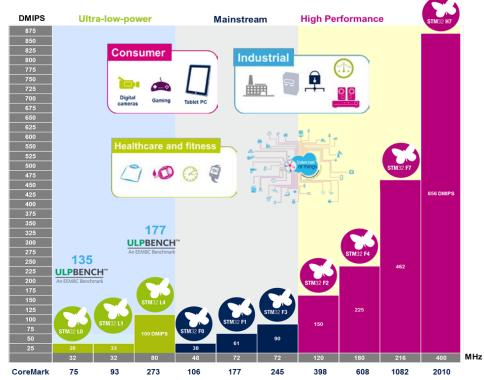

### STM32 ARM Cortex-M Based MCUs

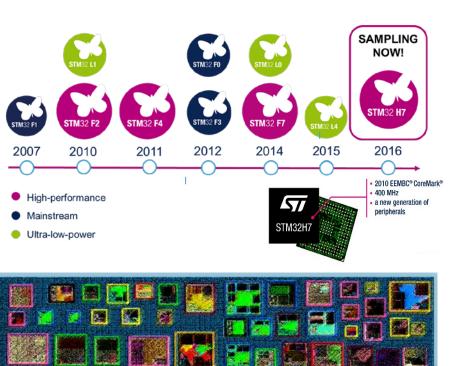

#### Keep Innovating!: Highest CoreMark Result on ARM Cortex-M

### STM32 MCU Design Challenges

#### **High Performance**

Performance:> 800 DMIPS

Dynamic Power efficiency

Static Power efficiency

Die size

#### **Ultra Low Power**

Dynamic Power efficiency

Static Power efficiency

Performance: > 100 DMIPS

Die size

#### Main Stream

Dynamic Power Efficiency

Ratio Performance/Power

Die Size

**Static Power Efficiency**

### 1. Power, Robustness, Size Co-Optimization

- Multi-VT / Multi-site / Multivoltage / Multi Process scenarios

- Ultra low power clock tree

- EMC , Robustness, Safety Compliancy

### 2. Multi-Voltage Design Complexity

- Fragmented voltage area hierarchically/topologically

- Voltage scaling

- Always On Cells (isolated / not isolated)

## 3. System Performances & ARM Cortex-M Cores integration Objectives

- Realizing maximum system performance

- Achieving ultra-low power

Broad diversity of challenges, very aggressive time schedules